Vhdl Code For Parity Bit Generator

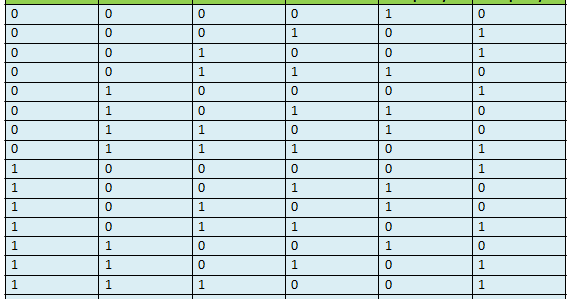

The ’AC280 and ’ACT280 are 9-bit odd/even parity genera-tor/checkers that utilize Advanced CMOS Logic technology. Both even and odd parity outputs are available for checking or generating parity for words up to nine bits long. Even par-ity is indicated (∑E output is HIGH) when an even number of data inputs is HIGH. VHDL 2008 standard offers a new xor operator to perform this operation. Much more simple than the traditional solution offered by Aaron. Signal Data: std_logic_vector(3 downto 0); signal Parity: std_logic;...

Hello, Does the below look like acceptable vhdl code for the 8 bit even parity check? CODE: library IEEE; use IEEE.STDLOGIC1164.ALL; use IEEE.STDLOGICARITH.ALL; use IEEE.STDLOGICUNSIGNED.ALL; entity pairity is generic(n:integer:=7); port(a:in stdlogicvector(n-1 downto 0); b:out stdlogicvector(n downto 0)); end pairity; architecture Behavioral of pairity is begin process(a) variable temp1:stdlogic; variable temp2:stdlogicvector(b'range); begin temp1:='0'; for i in a'range loop temp1:=temp1 xor a(i); temp2(i):=a(i); end loop; temp2(b'high):=temp1; b.